# IOWA STATE UNIVERSITY Digital Repository

Graduate Theses and Dissertations

Iowa State University Capstones, Theses and Dissertations

2013

# Accurate spectral test algorithms with relaxed instrumentation requirements

Siva Kumar Sudani Iowa State University

Follow this and additional works at: https://lib.dr.iastate.edu/etd Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Sudani, Siva Kumar, "Accurate spectral test algorithms with relaxed instrumentation requirements" (2013). *Graduate Theses and Dissertations*. 13459. https://lib.dr.iastate.edu/etd/13459

This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digirep@iastate.edu.

## Accurate spectral test algorithms with relaxed instrumentation requirements

by

## Sudani Siva Kumar

A dissertation submitted to the graduate faculty

in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Major: Electrical Engineering

Program of Study Committee: Randall Geiger, Co-major Professor Degang Chen, Co-major Professor Nathan Neihart Sumit Chaudhary Simon Laflamme

> Iowa State University Ames, Iowa 2013

Copyright © Sudani Siva Kumar, 2013. All rights reserved.

## DEDICATION

This work is dedicated to my wife Yenumula Vanaja for staying with me throughout the course of PhD with patience and love and to my dad Sri Sudani Satyanarayana and my mother Smt. Sudani Bala Kumari for believing in me and sending me abroad to pursue my PhD.

## TABLE OF CONTENTS

| DEDICA | TION                                                                                                            | ii |

|--------|-----------------------------------------------------------------------------------------------------------------|----|

| ACKNO  | WLEDGEMENTS                                                                                                     | v  |

| ABSTRA | АСТ                                                                                                             | vi |

| CHAPTE | ER 1 INTRODUCTION                                                                                               | 1  |

| I.     | Motivation                                                                                                      | 1  |

| II.    | IEEE Standard ADC Spectral Test                                                                                 | 6  |

| III.   | Challenges in ADC Spectral Test                                                                                 | 11 |

| IV.    | Dissertation Organization                                                                                       | 12 |

|        | References                                                                                                      | 14 |

|        | ER 2 FIRE: A FUNDAMENTAL IDENTIFICATION AND<br>EMENT METHOD FOR ACCURATE SPECTRAL TEST WITHOUT<br>ING COHERENCY | 17 |

| I.     | Introduction                                                                                                    | 17 |

| II.    | Issues with non-coherent sampling                                                                               | 22 |

| III.   | Fundamental Identification and Replacement (FIRE) method                                                        | 24 |

| IV.    | Simulation Results                                                                                              | 35 |

| V.     | Measurement Results                                                                                             | 41 |

| VI.    | Conclusion                                                                                                      | 47 |

| VII.   | Acknowledgments                                                                                                 | 48 |

|        | References                                                                                                      | 48 |

|        | T TO SIMULTANEOUS NON-COHERENT SAMPLING AND                                                                     |    |

| AMPLIT | UDE CLIPPING                                                                                                    | 52 |

| I.     | Introduction                                                                                                    | 52 |

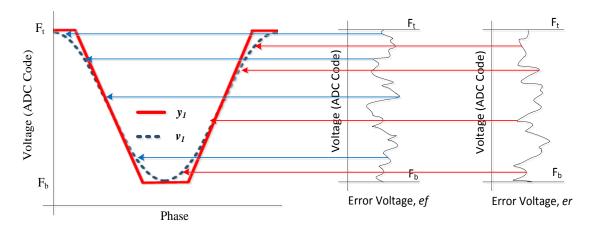

| II.    | Effect of non-coherent sampling and ADC clipping                                                                | 55 |

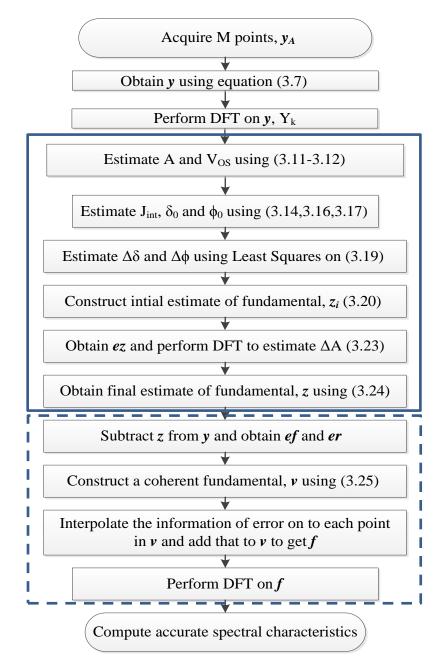

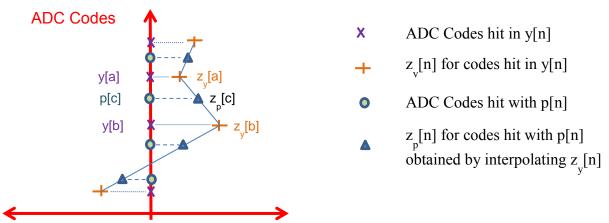

| III.   | Fundamental estimation, removal and residue interpolation (FERARI)                                              |    |

|        | method                                                                                                          | 60 |

| IV.    | Simulation Results                                                                                              | 74 |

| V.     | Measurement Results                                                                                             | 80 |

| VI.    | Conclusion                                                                                                      | 84 |

| VII.   | Acknowledgments                                                                                                 | 85 |

|        | References                                                                                                      | 85 |

# Page

| )     |

|-------|

| 88    |

| 88    |

| ce 91 |

| 100   |

| 112   |

| 116   |

| 117   |

| 117   |

|       |

|       |

| 120   |

| 121   |

| 123   |

| 125   |

|       |

| 127   |

| out   |

| 138   |

| 153   |

| 153   |

|       |

| 156   |

|       |

|       |

|       |

#### ACKNOWLEDGEMENTS

I would like to take this opportunity to express my thanks to all those who helped me during the course of my doctoral studies.

First, I would like to thank my major professors Dr. Randall Geiger and Dr. Degang Chen for giving me an opportunity to pursue PhD at Iowa State University. I am grateful to them for their continual guidance and support throughout my course of study. It was a great learning experience to work with both of them as it not only enhanced my knowledge in design and test of circuits, but also helped me gain new problem solving skills.

I would also like to thank my committee members: Dr. Nathan Neihart, Dr. Sumit Chaudhary, Dr. Y. T. Poon and Dr. Simon Laflamme for their precious time, advice and contributions to this work.

I would like to thank my friends – Sriram Reddy, Bharath Vasan, Rakesh Mahadevapuram, Prasad Avirneni, Sambit Pattnaik, Srivani Harish, Vishwanath Somasekar, Ganesh Rokkam, Siva Konduri, Prem Ramesh and Sankalp organization for making my stay in Ames lively. I would also like to thank my colleagues Tao Zeng, Jingbo Duan, Chen Zhao, Tina Wang, Vaibhav Kumar, Jake Sloat, Li Xu and Minshun Wu for their support.

Finally, I would like to thank my wife, Y. Vanaja (Munny), for leaving a wonderful job to stay with me in Ames. Thanks for all the sacrifices and support throughout my PhD and for being there when needed.

#### ABSTRACT

Spectral testing is widely used to test the dynamic linearity performance of Analog-to-Digital Converters (ADC) and waveform generators. Dynamic specifications for ADCs are very important in high speed applications such as digital communications, ultrasound imaging and instrumentation. With improvements in the performance of ADCs, it is becoming an expensive and challenging task to perform spectral testing using standard methods due to the requirement that the test instrumentation environment must satisfy several stringent conditions. In order to address these challenges and to decrease the test cost, in this dissertation, three new algorithms are proposed to perform accurate spectral testing of ADCs by relaxing three necessary conditions required for standard spectral testing methods. The testing is done using uniformly sampled points.

The first method introduces a new fundamental identification and replacement (FIRE) method, which eliminates the requirement of coherent sampling when using the DFT for testing the spectral response of an ADC. The robustness and accuracy of the proposed FIRE method is verified using simulation and measurement results obtained with non-coherently sampled data.

The second method, namely, the Fundamental Estimation, Removal and Residue Interpolation (FERARI) method, is proposed to eliminate the requirement of precise control over amplitude and frequency of the input signal to the ADC. This method can be used when the ADC output is both non-coherently sampled and clipped. Simulation and measurement results using the FERARI method with non-coherently sampled and clipped outputs of the ADC are used to validate this approach.

A third spectral test method is proposed that simultaneously relaxes the conditions of using a spectrally pure input source and coherent sampling. Using this method, the spectral characteristics of a high resolution ADC can be accurately tested using a non-coherently sampled output obtained with a sinusoidal input signal that has significant and unknown levels of nonlinear distortion. Simulation results are presented that show the accuracy and robustness of the proposed method.

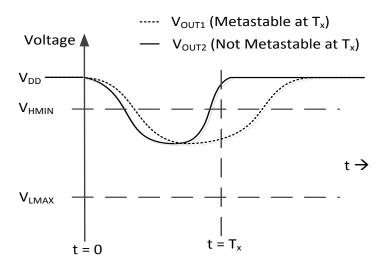

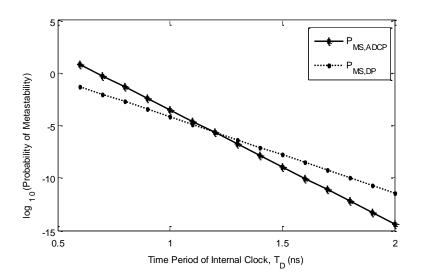

Finally, the issue of metastability in comparators and Successive Approximation Register (SAR) ADCs is analyzed. The analysis of probability of metastability in SAR ADCs with and without using metastable detection circuits is provided. Using this analysis, it is shown that as the frequency of sampling clock increases, using a metastable detection circuit decreases the probability of metastability in SAR ADCs.

# **CHAPTER I**

# INTRODUCTION

In this dissertation, methods for accurate spectral testing with relaxed requirements on test setup instrumentation are presented. The proposed methods are compared with standard test methods such as the IEEE standard that is widely used throughout the industry, windowing techniques, and the four parameter sine fitting method. It is shown that the proposed methods can accurately perform spectral testing even after relaxing some of the stringent (and expensive) conditions that are required for standard testing approaches. The methods are applicable for high performance Analog-to-Digital Converter (ADC) testing and high performance waveform generator testing. In the next three chapters, three methods are presented that perform spectral testing with accuracy and efficiency.

In this chapter, motivation to perform low-cost testing is provided followed by an overview of the IEEE standard method to perform spectral test. The challenges involved in performing spectral testing of high performance ADCs and a brief summary about the organization of this dissertation are presented.

#### I. MOTIVATION

Modern device technology requirements and advancements in semiconductor processing technologies are causing the density of gates in a silicon wafer to continuously grow at a rapid rate. This rapid growth is widely viewed as the trend in the semiconductor industry predicted by Moore's law. This enables designers to

economically and efficiently design a system with several high-complexity functional blocks on a single chip, often called System-on-Chip (SoC) [1]. The performance of stand-alone parts has also been increasing with developments in semiconductor technology. However, this increase in performance of stand-alone parts and increases in size and complexity in the design of SoCs has introduced several significant challenges for testing the parts or systems.

Production testing of stand-alone parts is performed to examine if the part meets a set of design specifications or performance requirements. The part is marked as a good part or a bad part depending on the positive or negative outcome of the production test. With increases in the performance of stand-alone parts, it is becoming a challenge to economically procure high accuracy test equipment to perform conventional tests. Paralleling this challenge are dramatic increases in the cost of testing. Therefore, there is an imminent need to develop new test methods that can reduce test costs by using lowend measurement setups to accurately test high performance parts.

SoCs are gaining popularity and becoming more favorable for production as they decrease the design cost by allowing the whole system to be designed on a single chip. SoCs are typically comprised of several complex sub circuits and it is usually essential to individually test all sub circuits in the system to guarantee the specified system performance. It is challenging to de-embed each block separately for testing the sub circuits on the SoC due to dense integration and local loading and this further leads to increases in test costs. One solution to testing SoCs cost effectively is to use Built-in Self-Test (BIST) circuits. When BIST is employed, the test circuitry is also present on

the same chip as the Device under Test (DUT). With a BIST solution, the challenges associated with de-embedding each block can be reduced or eliminated. However, economical constraints dictate that the test circuitry in BIST circuits should have negligible area compared to that of the DUT. If conventional test methods are used in BIST circuits for testing analog functions, the test circuitry often must include high accuracy, spectrally pure, or high linear stimulus signal generators. These highperformance signal generators invariably necessitate a substantial design effort and require a large area. In some cases, the area required by the test circuitry could be more or even much more than that of the DUT. In almost all applications, a large area requirement for BIST circuits would be unacceptable. As a result, for BIST circuits to be practical, new test methods need to be developed that can relax the conditions on test setup measurement so that low-end measurement systems can be designed on-chip and still provide accurate test results. The International Technology Roadmap for Semiconductors also recognizes the need and suggested that more research needs to be done on BIST for analog and mixed-signal circuits.

Analog-to-Digital Converters are one of the most widely used integrated circuits. They are not only used as stand-alone parts but are also widely used in the analog front end in SoCs [2]. ADCs are usually tested for static parameters such as Integral Nonlinearity (INL), Differential Non-linearity (DNL), offset, gain, etc. They are also tested for dynamic parameters such as Total Harmonic Distortion (THD), Spurious Free Dynamic Range (SFDR), Signal to Noise Ratio (SNR), etc. [3].

Conventional data converter testing methods have changed little over the past three decades. When these testing methods evolved, the performance of the best ADCs available from industry was modest by today's standards and the cost of computing equipment and computing time was very high. As a consequence, a good testing solution at the time was based upon using a reasonably good signal generator and minimal post-processing of measurement data by a computer. In the intervening three decades there have been dramatic changes in both performance and cost structures. The performance of ADCs has dramatically increased, the cost of high-end analog test equipment used to generate test signals for testing ADCs has increased dramatically, but the cost of computational equipment and computational operations has dropped at a much higher rate. So, the question naturally arises, about whether new methods for testing high performance ADCs that are no longer constrained by the cost of computational equipment and computational operations can be developed that can modestly or even dramatically reduce the cost of testing high performance ADCs.

To decrease the test cost of ADCs, new methods are needed that can decrease the measurement setup cost by relaxing the stringent conditions required for conventional instruments used for testing ADCs and, if necessary, increasing or dramatically increasing the use of computational tools as a part of the testing flow. In [4], a Stimulus Error Identification and Removal (SEIR) method was proposed that can relax the requirement of high linear stimulus to perform static Integral Nonlinearity (INL) and Differential Nonlinearity (DNL) linearity testing. With the SEIR approach, a tradeoff was made between linearity of the stimulus signal and the number of computational

operations that can provide a dramatic overall reduction in test costs. In this dissertation, work has been done to relax three stringent conditions (on the test setup) that are required to perform accurate dynamic spectral testing of an ADC and these three conditions are the major contributors to the high test costs with conventional testing approaches. Paralleling the relaxation of the performance requirements for the signal generator has been a significant increase in the computational complexity of the testing algorithm. But as with the SEIR approach, the tradeoffs between test equipment specifications and computational time will provide a dramatic overall reduction in spectral testing costs in today's environment.

It should be noted here that the focus in this dissertation on ADC testing has been chosen only for convenience. The same methods can also be used to perform spectral testing of waveform generators.

Dynamic testing of ADCs is often called spectral testing or AC testing and includes testing of the ADCs dynamic (frequency dependent) specifications. In contrast, full spectrum testing not only tests dynamic specifications but also focuses on testing all spectral bins including harmonic and non-harmonic bins. Being able to perform full spectrum testing is especially important for systems whose Spurious Free Dynamic Range (SFDR) is limited by non-harmonic spurious tones, such as time-interleaved ADCs. The test setup for both spectral test and full spectrum test is the same.

#### II. IEEE STANDARD ADC SPECTRAL TEST

The IEEE standard for Digitizing Waveform Recorders (IEEE Std. 1057) [5] and IEEE standard for Terminology and Test Methods for Analog-to-Digital Converters (IEEE Std. 1241) [6] specifies that the test setup should satisfy the following five conditions for accurately performing the spectral testing of ADCs. Firstly, the spectral purity of the input signal to ADC should be about 3 to 4 bits more pure than the ADC under test. In other words, to test an N-bit ADC, the input signal should be more than N+3 bits pure. The second condition is that the peak-to-peak voltage of the input signal should be slightly lower than the ADC input range so that the output of the ADC is not clipped. The third condition is that, if possible, the input signal be coherently sampled. Finally, the total number of sampled points (or data record length) should be sufficiently large.

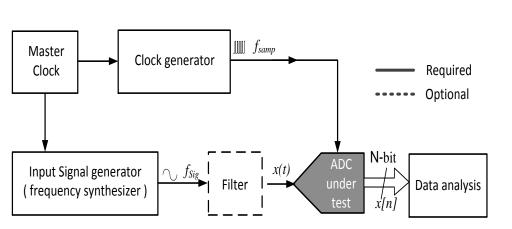

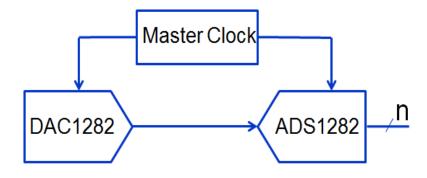

Fig. 1.1 shows the recommended test setup for standard spectral testing of an Nbit ADC. The setup consists of a master clock that controls the frequency of both the clock signal and the input signal. This can provide coherent sampling. Occasionally, there is a filter present between the input signal source and the ADC under test. The filter is added to improve the spectral purity of the input signal to the ADC. The amplitude of the input signal is selected such that the peak-to-peak value of input to ADC is within the ADC input range. Care is also taken to obtain very small relative jitter between the input and clock signals using low jitter clock generators. Using this setup, the output of ADC is

acquired and analyzed for spectral parameters of the ADC under test. In this section, it is considered that all the above conditions are satisfied.

Let  $f_{Sig}$  be the frequency of input signal,  $f_{Samp}$  be the clock frequency, M be the total number of data points recorded to measure the spectral characteristics and J be the total number of periods of the input signal sampled in the recorded data. The four parameters are related by equation (1.1).

Figure 1.1: Setup to test ADC Spectral characteristics

The sampling is said to be coherent if J in (1.1) is an integer that is co-prime with M and non-coherent if J is a non-integer. In addition, it is recommended that J > 5 [6].

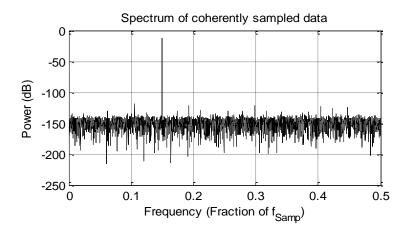

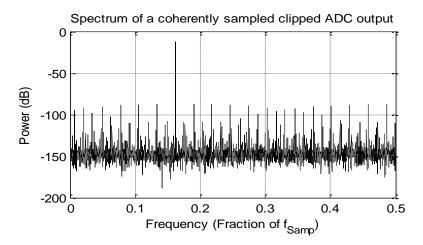

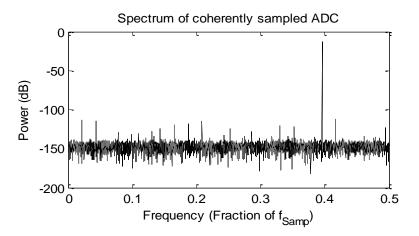

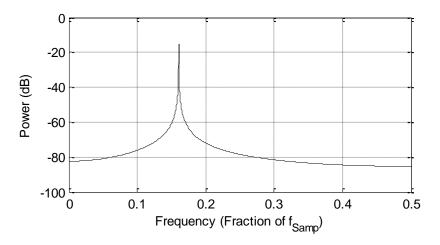

It is recommended to perform coherent sampling to accurately test an ADC. Fig. 1.2 shows the spectrum of an example ADC when sampled coherently. It can be seen from Fig. 1.2 that the spectrum is clean and all the spectral parameters such as, THD, SFDR and SNR, can be accurately estimated as explained below.

Figure 1.2: Power Spectrum of a coherently sampled ADC Output

Assume x(t) is the time domain representation of the analog input signal. The signal is ideally a pure sine wave and is given by equation (1.2).

$$x(t) = A\cos\left(2\pi f_{sig}t\right) \tag{1.2}$$

where, *A* is the amplitude of x(t).

Let x[n] be the analog interpretation of the digital output obtained from the ADC whose gain error and offset have been calibrated. x[n] can be represented by (1.3).

$$x[n] = A\cos\left(\frac{2\pi J}{M}n + \phi\right) + \sum_{h=2}^{H} A_h \cos\left(\frac{2\pi h J}{M}n + \phi_h\right) + w[n]$$

(1.3)

for n = 0,1,2,...,*M*-1.  $\phi$  is the initial phase of the sampled *x*(*t*). *M* is usually selected to be a power of 2 for faster processing of the Discrete Fourier Transform (DFT) with the Fast Fourier Transform (FFT) algorithm. *H* is the total number of harmonics considered in *x*[*n*], *A<sub>h</sub>* and  $\phi_h$  are the amplitude and initial phase of *h*<sup>th</sup> harmonic respectively. It is assumed that *A<sub>h</sub>* << *A* and  $\phi_h \in [0,2\pi)$  for all  $2 \le h \le H$ . *w*[*n*] corresponds to white noise

in  $n^{th}$  sample which can be due to quantization noise, input referred ADC noise and additive noise in the input signal. The harmonics in the output of ADC, x[n], are attributable to the distortion of ADC. Actually, there are an infinite number of harmonics. But, for analysis purposes, only the first H harmonics are considered throughout this dissertation. This is a justifiable assumption since the higher order harmonics in a real ADCs usually have negligible power.

The spectral parameters can be accurately obtained by taking DFT of M coherently sampled data points. The DFT of x[n] is given by equation (1.4).

$$X_{k} = \frac{1}{M} \sum_{n=0}^{M-1} x[n] e^{-j\frac{2\pi k}{M}n}, \text{ for } k = 0, 1, 2, ..., M-1$$

(1.4)

where *k* represents the frequency bin's index. For example, with coherent sampling, k = h\*J represents the frequency bin of the h<sup>th</sup> harmonic and if h = I, k = J represents the frequency bin of the fundamental.  $X_0$  corresponds to the DC component in signal x[n]. Other values of *k* correspond to noise.

From equations (1.3) and (1.4), neglecting the effect of noise,  $X_k$  can be rewritten and given as (1.5).

$$X_{k} = \begin{pmatrix} \frac{A}{2M} \left\{ \frac{\sin(\pi(J-k))}{\sin(\frac{\pi(J-k)}{M})} e^{j(a(J-k)+\phi)} + \frac{\sin(\pi(J+k))}{\sin(\frac{\pi(J+k)}{M})} e^{-j(a(J+k)+\phi)} \right\} \\ + \frac{H}{h=2} \frac{A_{h}}{2M} \left\{ \frac{\sin(\pi(hJ-k))}{\sin(\frac{\pi(hJ-k)}{M})} e^{j(a(hJ-k)+\phi_{h})} + \frac{\sin(\pi(hJ+k))}{\sin(\frac{\pi(hJ+k)}{M})} e^{-j(a(hJ+k)+\phi_{h})} \right\} \end{pmatrix}$$

(1.5)

It can be seen from (1.5) that, for coherent sampling,

$$X_{J} = \frac{A}{2}e^{j\phi}$$

and  $X_{hJ} = \frac{A_{h}}{2}e^{j\phi_{h}}$  (1.6)

For other values of k,  $X_k$  represents the noise as there is no contribution from the fundamental and harmonics on the bins if the M points are coherently sampled. The power of fundamental, h<sup>th</sup> harmonic and noise in coherently sampled data can be accurately estimated as  $P_1$ ,  $P_h$  and  $P_{noise}$  respectively using (1.7),

$$P_{1} = 2|X_{J}|^{2} = \frac{A^{2}}{2}; \qquad P_{h} = 2|X_{hJ}|^{2} = \frac{A_{h}^{2}}{2}; \qquad P_{noise} = \sum_{\substack{k=1\\k\neq J,hJ\\h=2,3,\dots,H}}^{M-1} |X_{k}|^{2}$$

(1.7)

From (1.7), the spectral parameters such as THD, SNR and SFDR for a coherently sampled signal can be calculated using equations in (1.8).

$$THD = \frac{\sum_{h=2}^{H} P_h}{P_1}; \quad SNR = \frac{P_1}{P_{noise}}; \quad SFDR = \frac{P_1}{2 * \max_{\substack{k=1,\dots,M/2\\k \neq J}} \left( \left| X_k \right|^2 \right)}$$

(1.8)

The equations (1.6-1.8) give accurate values of spectral parameters. Also, since the power of each frequency bin can be obtained accurately, this coherent sampling method can be used for full spectrum testing.

The challenges in performing high performance ADC spectral test using standard methods are discussed in the following section.

#### III. CHALLENGES IN ADC SPECTRAL TEST

As mentioned in section I, there are five conditions that need to be satisfied to perform standard ADC spectral testing. It can be said that the first four conditions are challenging to achieve as the performance of ADC continuously increases.

The first condition is to use a very highly pure sinusoid signal source as input to the ADC under test. This condition requires either new methodologies to design highly pure signal sources or several filters to suppress the unwanted harmonics. Both solutions lead to high test cost. Also, as noted earlier, for BIST ADCs, the area required to design highly linear signal sources could be very large leading to high costs.

The second condition is to be able to control the amplitude so that the peak-topeak voltage of the input signal is within the input range of the ADC. This condition could be a challenging task in BIST circuits as precise control over amplitude of the signal is not possible. With trend shifting towards designing BIST ADCs, it is important to be able to test the ADC characteristics from clipped output data.

The next condition is to have minimal relative jitter between the input signal and the clock signal. This requires high accuracy clock and signal generators, which could increase the test cost with increase in ADC performance.

The fourth condition is to sample the input signal coherently. Achieving coherent sampling is one of the major bottlenecks in performing spectral testing. In order to achieve coherent sampling, it is required to use high accuracy signal generators or Phase Locked Loops (PLL). This results in additional hardware which adds to the total ADC test cost. Also, in BIST applications, it is impractical to achieve coherent sampling as PLLs or high accuracy frequency synthesizers cannot be economically designed on-chip (as they increase the test circuitry area which results in additional cost).

In order to decrease the production test cost and to make BIST ADCs practical, it is required to design new test methods that can relax the above stringent conditions to perform accurate ADC spectral test. In this dissertation, three methods are proposed to relax some of the aforementioned challenging conditions for ADC spectral test.

#### IV. DISSERTATION ORGANIZATION

Three new test methods that address the aforementioned challenges to perform spectral testing are presented in this dissertation. As mentioned earlier, the methods can be applied to test high performance ADCs or high performance waveform generators. These methods can be used either in production testing or in BIST applications to decrease the test cost. The dissertation is arranged in the following order.

In Chapter 2, a method called the Fundamental Identification and Replacement (FIRE) method is presented. With FIRE, the requirement of coherent sampling to perform accurate ADC spectral testing [7-10] is completely eliminated. A new approach to identify the fundamental in a non-coherently sampled data set using frequency domain data and Newtons method is proposed. Though non-coherent, the samples must be uniformly spaced. The validity of the method is shown using measurement data from commercially available high resolution ADCs. The use of this method can decrease the test costs associated with achieving coherent sampling.

In Chapter 3, the Fundamental Estimation, Removal And Residue Interpolation (FERARI) method is presented [11-12]. This method simultaneously relaxes the requirement to have precise control over amplitude and frequency of the input signal in order to test ADCs. A new fundamental estimation technique is proposed that can be used when the ADC output is clipped and is sampled non-coherently with uniform spacing. Measurement results are provided to validate this method using a commercially available 16-bit ADC. The method can be used in BIST applications as precise amplitude and frequency control is costly to achieve in such systems.

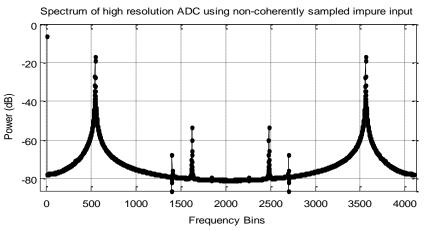

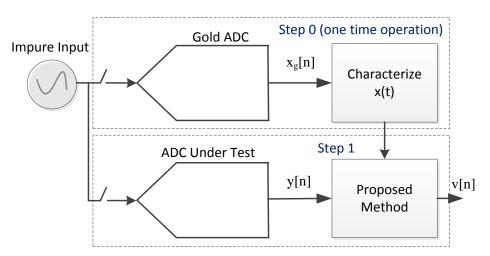

In Chapter 4, a method of relaxing the conditions of using a spectrally pure sinusoidal input source and simultaneously removing the requirement of coherent sampling is proposed [13-14]. The sampled points need to be uniformly spaced. The non-linear (impure) input that is non-coherently sampled is first characterized using a "Golden ADC". Later, the same input signal is used to test high resolution ADCs accurately. This method is explained in detail in this chapter. The simulation results

show accurate functionality and robustness of the proposed method. This method can be used to decrease the test cost in production testing, where acquiring a source with high spectral purity and obtaining coherent sampling result in high test costs.

In chapter 5, the work done on Metastability in comparators and ADCs is discussed [15]. A rigorous mathematical definition of metastability is presented. The probability of metastability is analyzed and compared for two comparator architectures, one with a latch and the other with a latch followed by an inverter. The probability of metastability of synchronous SAR ADCs with and without using metastable detection circuit is analyzed and compared. The analysis can be used to decide if a metastable detection circuit is necessary to decrease the probability of metastability in SAR ADCs.

#### References

- Y. Chen, S. Kung, "Trends and challenges with system-on-chip technology for multimedia system design," *Emerging Information technology Conference*, 2005, vol., no., pp.4, 15-16 Aug. 2005.

- [2] Bult, K., "Embedded Analog-to-Digital Converters," Solid State Device Research Conference, 2009. ESSDERC '09. Proceedings of the European, vol., no., pp.72,84, 14-18 Sept. 2009

- [3] M. Burns, G.W. Roberts, "An Introduction to Mixed-Signal IC Test and Measurement", Oxford University Press, New York, USA, 2000.

- [4] L. Jin, K. Parthasarathy, T. Kuyel, D. Chen, R. Geiger, "Accurate testing of analogto-digital converters using low linearity signals with stimulus error identification and

removal," *Instrumentation and Measurement, IEEE Transactions on*, vol.54, no.3, pp.1188,1199, June 2005

- [5] IEEE Standard for Digitizing Waveform Recorders-IEEE Std. 1057-2007.

- [6] IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters, IEEE Std. 1241-2010

- [7] S. Sudani, D. Chen, R. Geiger, "A 2-FFT method for on-chip spectral testing without requiring coherency," *Instrumentation and Measurement Technology Conference* (*I2MTC*), 2011 IEEE, vol., no., pp.1,6, 10-12 May 2011

- [8] S. Sudani, M. Wu, D. Chen, "A novel robust and accurate spectral testing method for non-coherent sampling," *Test Conference (ITC), 2011 IEEE International*, vol., no., pp.1,10, 20-22 Sept. 2011

- [9] S. Sudani, D. Chen, R. Geiger, "A method for accurate full spectrum testing without requiring coherency," *Circuits and Systems (MWSCAS), 2012 IEEE 55th International Midwest Symposium on*, vol., no., pp.346,349, 5-8 Aug. 2012

- [10] S. Sudani, D. Chen, "FIRE: A Fundamental Identification and Replacement Method for accurate spectral test without requiring coherency," Accepted for publication in *Transactions on Instrumentation and Measurement – 2013*

- [11] S. Sudani, L. Xu, D. Chen, "Accurate Full Spectrum Test Robust to Simultaneous Non-coherent sampling and amplitude clipping," *Test Conference* (*ITC*), 2013 IEEE International

- [12] L. Xu, S. Sudani, D. Chen, "Accurate spectral testing wih clipped and noncoehrently sampled data," Under second revision at *Transactions on Instrumentation and Measurement 2013*.

- [13] S. Sudani, D. Chen, R. Geiger, "High resolution ADC spectral test with known impure source and non-coherent sampling," *International Symposium on circuits and systems (ISCAS) – 2013*, Beijing, China

- [14] S. Sudani, D. Chen, R. Geiger, "A low cost method to test high resolution ADCs using non-linear input and non-coheren sampling," To be submitted to *Transactions* on Circuits and Systems, Regular Papers – 1, 2013

- [15] S. Sudani, R. Geiger, "Analysis of probability of metastability in comparators and successive approximation register ADCs," To be submitted to *Transactions on Circuits and Systems, Regular Papers – 1, 2013.*

# **CHAPTER 2**

# FIRE: A FUNDAMENTAL IDENTIFICATION AND REPLACEMENT METHOD FOR ACCURATE SPECTRAL TEST WITHOUT REQUIRING COHERENCY

Achieving coherent sampling is one of the major bottlenecks to perform ADC spectral test, especially when high-precision instruments or high-performance frequency synthesizes are not readily available. If coherent sampling is not achieved, there could be huge leakage in the spectrum which might lead to inaccurate test results. In this chapter, a new Fundamental Identification and Replacement method is presented that can completely eliminate the need for coherent sampling in spectral testing. A 2-step Fundamental Identification method is used to very accurately estimate the non-coherent fundamental. Extensive simulation results show the functionality and robustness of the method. Measurement results obtained in industry labs using commercially available high resolution ADCs successfully validate the proposed method for both accuracy and robustness.

## I. INTRODUCTION

In chapter 1, it was recommended to achieve coherent sampling to obtain accurate spectral results of an ADC. However, to achieve coherent sampling, it is required to obtain high accuracy frequency synthesizers and Phase Locked Loops (PLL). This results in increase in test cost and test area.

Another case is, during characterization of an ADC, the spectral characteristics of the ADC at various input frequencies need to be tested. It would take more test time to achieve coherent sampling in such cases as the frequencies of input signal and clock signal need to be tuned for each input frequency separately to achieve coherent sampling. This tuning increases the test cost and the product delivery time.

Also looking into the future, there is a strong drive to design circuits that have Built-in Self-Test (BIST) capability to decrease the test cost. The area required by the testing circuitry should be very small compared to that of the Device under Test (DUT). In such circuits, it is impossible to achieve coherent sampling with a self-contained oscillator as signal source implemented on a very small area.

In the above mentioned cases, it is either expensive or more time consuming or impossible to achieve coherent sampling. So, there is a strong need to develop new low cost test methods that can eliminate the condition of coherent sampling and still provide accurate spectral results.

#### A. State of the art methods for Non-coherent sampling

The state-of the-art methods proposed in the literature to perform accurate spectral test using non-coherently sampled data are discussed below.

#### 1) Windowing technique

Windowing technique is one of the widely used methods to obtain spectral characteristics from a non-coherently sampled data [1-6]. To obtain accurate spectral results with windows, the spectral power of secondary lobes of selected window should

be lower than the noise power of the ADC under test. This requires prior knowledge about the type of window to be used to accurately test the ADC. If a window with power in secondary lobes greater than the noise floor of the ADC under test is used, inaccurate results of spectral parameters are obtained. As a result, the spectral characteristics obtained are window dependent. Also, for large non-coherent sampling and high resolution ADCs, not all windows can achieve accurate spectral results [7].

#### 2) Four parameter Sine Fitting technique

The four parameter sine fitting method is used to characterize analog-to-digital converters and digital oscilloscopes for THD and ENOB [8-11]. In this method, the time domain data is used to identify the four parameters in the non-coherently sampled fundamental, namely, frequency (f), amplitude, offset and phase. Since the time domain data is a non-linear function of frequency (f), a non-linear method such as Newton method is used to identify the above four parameters. With this, the power of fundamental can be accurately estimated. Now, the identified fundamental is removed from the data to obtain the residue. Later, using the frequency value (f) obtained from four parameter sine fitting, a three parameter fit (amplitude, phase, offset) on the residue is performed for each harmonic component (with frequencies 2f, 3f, ...). Once the powers of all harmonics are obtained, the spectral parameters such as THD and SNR can be estimated using equations (1.8).

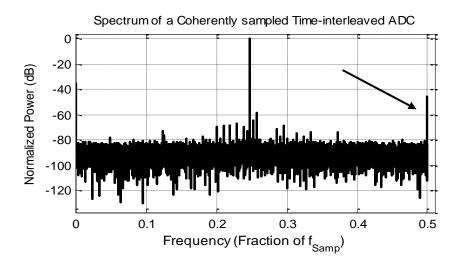

The four parameter sine fitting method gives accurate values of THD, SNDR and ENOB. Also, when the harmonic component determines SFDR, accurate value of SFDR is obtained. However, when a non-harmonic component determines SFDR as shown in

Fig. 2.1, the method cannot provide accurate value. In such cases, a method intended for full spectrum test is required. Furthermore, computational efficiency is one of the concerns when data record length is large. In [12], a multi-sine fitting algorithm was proposed to accurately estimate the fundamental and harmonics of the signal. However, the method also cannot provide accurate value of SFDR when a non-harmonic component has the highest power (excluding the fundamental) in the spectrum.

Figure 2.1: Power Spectrum of a coherently sampled time-interleaved ADC showing non-harmonic spur

#### 3) Other state-of the-art methods

In the recent past, several other methods have been proposed to relax the condition of coherency for spectral testing [13]. A 2-D FFT method was introduced in [14] with a time complexity of O ( $M^2log^2M$ ), where M is the total data record length. A singular value decomposition method was proposed in [15] which involve a time complexity of O ( $M^3$ ). In [16], a filter bank method was reported which results in an increase in testing circuitry area. A resampling technique was presented in [17], which

again results in increasing area due to additional decimator used. In [18-22], interpolating DFT (IpDFT) methods were used to eliminate the requirement of coherency. However, such methods cannot provide accurate value of SFDR when a non-harmonic spur dominates the harmonics. In [23], a fundamental identification and replacement method was proposed that can accurately estimate the spectral characteristics. However, the method is not robust to signal frequencies that are close to Nyquist range.

All the above methods suffer from one or more of the issues such as, large computation time, increase in area, lack of robustness across the Nyquist range, dependency of results on the type of window chosen or the inability to perform full spectrum test. So, it is required to develop a test method that can address all the above issues and accurately perform spectral test without requiring coherent sampling.

In [7], a Fundamental Identification and Replacement method was proposed that is robust over any level of non-coherency. The method provides accurate spectral results for ADCs with medium resolution. However, for very high resolution ADCs, the estimated spectral parameters have errors as the accuracy with which the fundamental was identified was not sufficient.

In this chapter, a new fundamental identification and replacement (FIRE) method that addresses all the above issues and performs accurate spectral testing is presented. Compared to the method in [7], a new 2-step fundamental identification method that can very accurately estimate the fundamental is proposed. The initial estimates of parameters are obtained in Step 1 using closed form expressions. In Step 2, Newton method is used

to accurately estimate all the parameters. The estimation is done using the frequency domain data and is computationally efficient. The estimated non-coherent fundamental is later removed from the initial data to obtain the residue. A fundamental that is coherently sampled is added to the residue and DFT is performed on the final data to obtain accurate spectral results. The functionality and robustness of proposed FIRE method is verified using both simulation and measurement data.

The remainder of the chapter is arranged as follows. The issue of Non-coherent sampling is described in Section II. Section III provides a detailed description of proposed FIRE method. Section IV presents the simulation results and Section V validates the FIRE method using measurement data. Section VI concludes the chapter.

#### II. ISSUES WITH NON-COHERENT SAMPLING

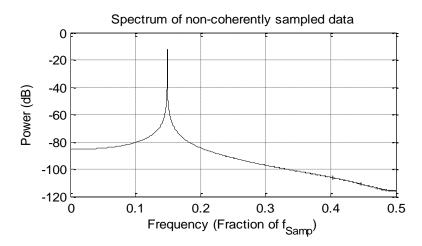

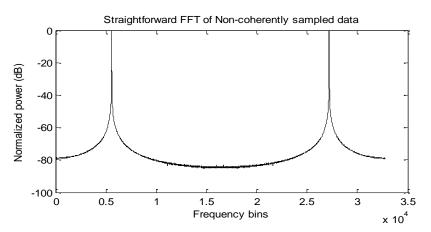

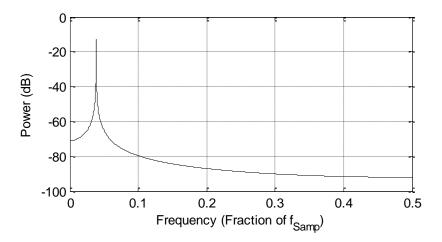

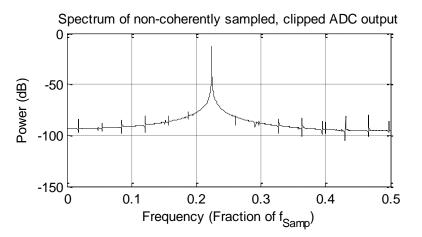

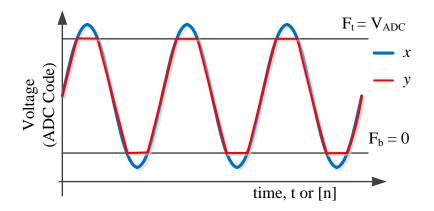

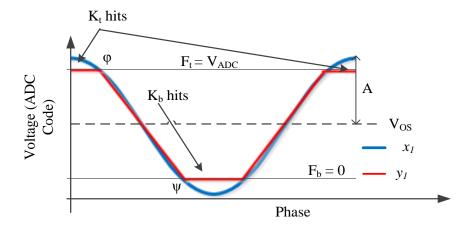

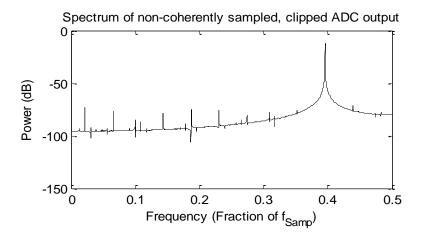

If the input signal is not coherently sampled, J in equation (1.3) is not an integer and as a result, the spectrum of such output data may contain severe skirting as shown in Fig. 2.2. This phenomenon is widely known as spectral leakage.

From chapter 1, let x(t) in (1.2) be the pure input source to the ADC. If the input is non-coherently sampled by the ADC, the output of ADC can be given by equation (2.1) (similar to equation 1.3) after calibrating gain error and offset. x[n] is the analog representation of the n<sup>th</sup> sampled digital output of ADC. All the parameters in (2.1) are similar to the parameters defined in chapter 1. x[n] is obtained after considering only the first H harmonics. It is assumed that the higher harmonics have negligible power.

Figure 2.2: Power spectrum of a non-coherently sampled ADC Output

$$x[n] = A\cos\left(\frac{2\pi J}{M}n + \phi\right) + \sum_{h=2}^{H} A_h \cos\left(\frac{2\pi h J}{M}n + \phi_h\right) + w[n]$$

(2.1)

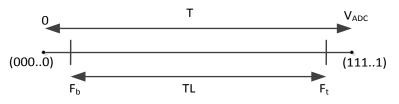

It should be noted that *J* in (2.1) is no longer an integer. Let  $J = J_{int} + \delta$ , where  $J_{int}$  represents the integer part of *J* and  $\delta$  represents the non-integer part of *J*.  $\delta$  varies from -0.5 to 0.5. The DFT of non-coherently sampled x[n] in (2.1) can be obtained using equation (2.2). Substituting non-integer *J* in (2.1) and (2.2), the k<sup>th</sup> DFT coefficient,  $X_k$ , can be given as (2.3).

$$X_{k} = \frac{1}{M} \sum_{n=0}^{M-1} x[n] e^{-j\frac{2\pi k}{M}n}, \text{ for } k = 0, 1, 2, ..., M-1$$

(2.2)

It can be seen that unlike in equation (1.5), the contribution from fundamental and harmonics on to other frequency bins is no longer zero in equation (2.3) due to the presence of non-integer  $\delta$ . As a result, using equations (1.6-1.8) to test spectral characteristics of a non-coherently sampled data, results in inaccurate values. Such cases

of non-coherent sampling are very common and it is important to design a test method that can perform full spectrum Test in spite of having non-coherent sampling.

$$X_{k} = \begin{pmatrix} \frac{A}{2M} \left\{ \frac{\sin\left(\pi\left(J_{\text{int}} + \delta - k\right)\right)}{\sin\left(\frac{\pi\left(J_{\text{int}} + \delta - k\right)}{M}\right)} e^{j\left(a\left(J_{\text{int}} + \delta - k\right)\right)} + \frac{\sin\left(\pi\left(J_{\text{int}} + \delta + k\right)\right)}{\sin\left(\frac{\pi\left(J_{\text{int}} + \delta + k\right)}{M}\right)} e^{-j\left(a\left(J + k\right) + \phi\right)} \right\} \\ + \frac{\frac{H}{h=2} \frac{A_{h}}{2M}}{2M} \left\{ \frac{\frac{\sin\left(\pi\left(hJ_{\text{int}} + h\delta - k\right)\right)}{\sin\left(\frac{\pi\left(hJ_{\text{int}} + h\delta - k\right)}{M}\right)} e^{j\left(a\left(hJ_{\text{int}} + h\delta - k\right) + \phi_{h}\right)}}{\sin\left(\frac{\pi\left(hJ_{\text{int}} + h\delta + k\right)\right)}{\sin\left(\frac{\pi\left(hJ_{\text{int}} + h\delta + k\right)\right)}{M}\right)} e^{-j\left(a\left(hJ_{\text{int}} + h\delta + k\right) + \phi_{h}\right)} \right\}} \right\}$$

(2.3)

## III. FUNDAMENTAL IDENTIFICATION AND REPLACEMENT (FIRE) METHOD

In this section, a test method is proposed that can take in non-coherently sampled ADC output and perform full spectrum test. Before describing the method in detail, a brief description about the foundation for Fundamental Identification and Replacement methods [7, 23-26] is presented.

It can be said that when DFT is applied on non-coherently sampled data, the leakage in the spectrum is mainly due to the fact that the fundamental component is noncoherently sampled. It can also be stated that for high resolution ADC testing, the leakage from any frequency bin (other than the fundamental) to any other frequency tone

is significantly below the total noise power of the ADC. This effect of non-coherent fundamental is shown in Fig. 2.3 and Fig. 2.4.

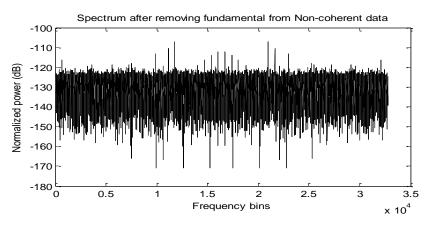

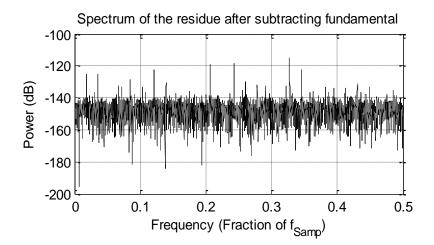

Fig. 2.3 is the spectrum of a non-coherently sampled data. As explained earlier, there is severe spectral leakage around the fundamental. However, it can be seen that if the non-coherent fundamental in this data is identified and removed, accurate information of harmonics and noise can be obtained from the spectrum of residue as shown in Fig. 2.4. So, it is required to accurately identify the non-coherent fundamental to obtain correct spectral results.

Figure 2.3: Spectrum of FFT of non-coherently sampled data showing leakage

Figure 2.4: Spectrum of residue obtained after removing the fundamental

#### A) Fundamental Identification

Several methods were presented in the past to identify the fundamental in a noncoherently sampled data [18-22, 27]. One of the proposed methods is the Interpolated Discrete Fourier Transform (IpDFT). The IpDFT methods start from applying windows on the non-coherently sampled data and later perform interpolation to accurately estimate the fundamental component [18-22]. In [22], a criterion to choose the optimal window to obtain accurate spectral characteristics was proposed. However, in the proposed FIRE method, the fundamental is identified from the DFT of non-coherently sampled data without using windows. As a result, the method is not dependent on windows and can accurately estimate the fundamental.

Substituting  $J = J_{int} + \delta$  in equation (2.1), in order to identify the fundamental in x[n], it is required to estimate the values of  $J_{int}$ ,  $\delta$ , A and  $\phi$ . In the proposed FIRE method, the fundamental component is identified in a two-step process. First step provides the value of  $J_{int}$  and initial estimates of  $\delta$ , A and  $\phi$  from the DFT of non-coherently sampled data. The second step obtains accurate estimates of  $\delta$ , A and  $\phi$  using Newton method. The procedure to identify the fundamental is explained in detail below.

1) First Step

The time domain output data of the ADC, x[n] in (2.1) is converted to frequency domain data by taking the DFT of x[n] which is given by  $X_k$  in equation (2.2). Using DFT coefficients, the value of  $J_{int}$  and initial values of  $\delta$ , A and  $\phi$  are estimated.

#### *a)* Estimate $J_{int}$ and $\delta$

$J_{int}$  is estimated by taking the index of frequency bin in half spectrum that contains the maximum power excluding the DC component and is given by (2.4).

$$J_{\text{int}} = \underset{1 \le k \le (M/2)}{\arg \max} \left| X_k \right|$$

(2.4)

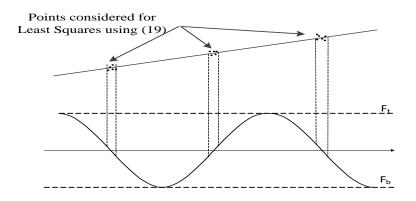

The initial value of  $\delta$  can be estimated with a three-point calibration method using the DFT coefficients. Using (2.3), for  $k = J_{int}$ ,  $X_k$  represents the DFT coefficient of the fundamental and for  $k = J_{int}+1$  and  $J_{int}-1$ ,  $X_k$  represents the DFT coefficients of the adjacent bins on either side of the fundamental bin. For high resolution ADCs, when estimating the fundamental, the effect of harmonics can be neglected. Also, in order to obtain a closed form expression for initial value of  $\delta$ , the term containing  $e^{-j(a(J+k+\delta)+\phi)}$ can be neglected compared to the term containing  $e^{j(a(J+k+\delta)+\phi)}$  for M > 1024 [28]. The neglected term is later considered in the equations to obtain an accurate estimate of  $\delta$  in the second step. After neglecting the above mentioned terms,  $X_k$  can be given by (2.5).

$$X_{k} \approx \frac{A}{2M} e^{j\phi} \frac{1 - e^{j2\pi(J-k)}}{1 - e^{j\frac{2\pi(J-k)}{M}}}$$

(2.5)

Let

$$Y = e^{j2\pi\delta}$$

(2.6)

For  $k = J_{int}$ ,  $J_{int}+1$  and  $J_{int}-1$ , using (2.5)

$$X_{J_{\text{int}}} = \frac{A}{2M} e^{j\phi} \frac{1 - e^{j2\pi\delta}}{1 - e^{j\frac{2\pi\delta}{M}}} = \frac{A}{2M} e^{j\phi} \frac{1 - Y}{1 - Y^{1/M}}$$

(2.7)

$$X_{J_{\text{int}}+1} = \frac{A}{2M} e^{j\phi} \frac{1 - e^{j2\pi\delta}}{1 - e^{j\frac{2\pi(\delta-1)}{M}}} = \frac{A}{2M} e^{j\phi} \frac{1 - Y}{1 - Y^{1/M} e^{-j\frac{2\pi}{M}}}$$

(2.8)

$$X_{J_{\text{int}}-1} = \frac{A}{2M} e^{j\phi} \frac{1 - e^{j2\pi\delta}}{1 - e^{j\frac{2\pi(\delta+1)}{M}}} = \frac{A}{2M} e^{j\phi} \frac{1 - Y}{1 - Y^{1/M} e^{j\frac{2\pi}{M}}}$$

(2.9)

The above three equations can be used to solve for *Y* in terms of  $X_{Jint}$ ,  $X_{Jint+1}$  and  $X_{Jint-1}$ .

$$Y^{1/M} = e^{j\frac{2\pi\delta}{M}} = \left(\frac{\frac{X_{J_{\text{int}}}}{X_{J_{\text{int}}+1}} - \frac{X_{J_{\text{int}}}}{X_{J_{\text{int}}-1}}}{\frac{X_{J_{\text{int}}}}{X_{J_{\text{int}}+1}} - \frac{X_{J_{\text{int}}}}{X_{J_{\text{int}}-1}} + e^{j\frac{2\pi}{M}} - e^{-j\frac{2\pi}{M}}}\right)$$

(2.10)

From equations 2.6 & 2.10, the initial value of  $\delta$ ,  $\delta_0$ , can be estimated by (2.11) as

$$\delta_{0} = \frac{M}{2\pi} imag \left( \ln \left( \frac{\frac{X_{J_{\text{int}}}}{X_{J_{\text{int}}+1}} - \frac{X_{J_{\text{int}}}}{X_{J_{\text{int}}-1}}}{\frac{X_{J_{\text{int}}}}{X_{J_{\text{int}}+1}} - \frac{X_{J_{\text{int}}}}{X_{J_{\text{int}}-1}} + e^{j\frac{2\pi}{M}} - e^{-j\frac{2\pi}{M}}} \right) \right)$$

(2.11)

#### b) Estimate A and $\phi$

Now that  $J_{int}$  and  $\delta$  are estimated, the initial values of A and  $\phi$  can be estimated using (2.7). Taking magnitude of  $X_{Jint}$  gives the initial value of A,  $A_0$ , as shown in equation (2.12).

$$A_{0} = 2M \left| X_{J_{\text{int}}} \right| \left| \frac{1 - e^{j\frac{2\pi\delta_{0}}{M}}}{1 - e^{j2\pi\delta_{0}}} \right|$$

(2.12)

The initial value of  $\phi$ ,  $\phi_0$ , can be estimated by using  $A_0$  and  $\delta_0$  as shown in equation (2.13).

$$\phi_0 = -imag\left(\ln\left(\frac{2MX_{J_{\text{int}}}}{A_0}\frac{1-e^{j\frac{2\pi\delta_0}{M}}}{1-e^{j2\pi\delta_0}}\right)\right)$$

(2.13)

Hence, using equations (2.4, 2.11-2.13),  $J_{int}$  and the initial values of  $\delta$ , A and  $\phi$  are estimated.

## 2) Second Step

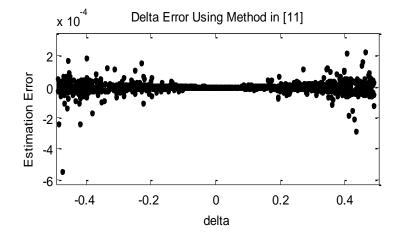

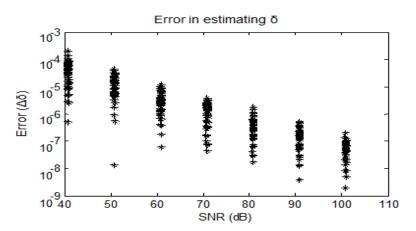

It can be noted that equation (2.5) involves an assumption to neglect  $e^{-j(a(J_{int}+k+\delta)+\phi)}$  term. The error in estimating the value of  $\delta$  for 1000 runs using this assumption is as shown in Fig. 2.5. It can be seen that the values of 1000 randomly selected  $\delta$ 's were estimated with a maximum error of about 10<sup>-4</sup>. However, to perform high resolution ADC test, the estimation error should be very small. Also, in order to propose a method that is independent of the resolution of ADC, the error should only be limited by the noise power per bin (i.e.,  $P_{noise}/M$ ). To obtain these requirements, it is necessary to include  $e^{-j(a(J_{int}+k+\delta)+\phi)}$  term in estimating the three parameters  $\delta$ , A and  $\phi$ . The expression of  $X_{Jint}$  without neglecting  $e^{-j(a(J_{int}+k+\delta)+\phi)}$  term is as shown below in (2.14). It can be shown that the expression is a non-linear equation in  $\delta$ . Also,  $X_{Jint}$  can

be represented with both real and imaginary parts given by  $R_{Jint}$  and  $I_{Jint}$  respectively as shown in (2.15). It should be noted that both  $R_{Jint}$  and  $I_{Jint}$  are functions of  $J_{int}$ , A,  $\delta$  and  $\phi$ .

$$X_{J_{\text{int}}} = \frac{A}{2M} e^{j\phi} \frac{1 - e^{j2\pi\delta}}{1 - e^{j\frac{2\pi\delta}{M}}} + \frac{A}{2M} e^{-j\phi} \frac{1 - e^{-j2\pi(2J_{\text{int}} + \delta)}}{1 - e^{-j\frac{2\pi(2J_{\text{int}} + \delta)}{M}}}$$

(2.14)

$$X_{J_{\text{int}}} = R_{J_{\text{int}}} \left( J_{\text{int}}, A, \delta, \phi \right) + j I_{J_{\text{int}}} \left( J_{\text{int}}, A, \delta, \phi \right)$$

(2.15)

Figure 2.5: Error in estimating  $\delta$  versus actual value of  $\delta$  using equation (2.11).

Similarly,  $X_{Jint+1}$  and  $X_{Jint-1}$  need to be modified from (2.8-2.9) to include the neglected term in (2.5). It can be seen that two equations are obtained by taking the real part and imaginary part of (2.15) separately. Doing the same for  $X_{Jint+1}$  and  $X_{Jint-1}$ , a total of six equations are obtained. Let the six equations be given as  $f_1,...,f_6$ . (2.16-2.21).

$$f_1(J_{\text{int}}, A, \delta, \phi) = R_{J_{\text{int}}}(J_{\text{int}}, A, \delta, \phi) - real(X_{J_{\text{int}}})$$

(2.16)

$$f_2(J_{\text{int}}, A, \delta, \phi) = I_{J_{\text{int}}}(J_{\text{int}}, A, \delta, \phi) - imag(X_{J_{\text{int}}})$$

(2.17)

$$f_3(J_{\text{int}}, A, \delta, \phi) = R_{J_{\text{int}}+1}(J_{\text{int}}, A, \delta, \phi) - real(X_{J_{\text{int}}+1})$$

(2.18)

$$f_4(J_{\text{int}}, A, \delta, \phi) = I_{J_{\text{int}}+1}(J_{\text{int}}, A, \delta, \phi) - imag(X_{J_{\text{int}}+1})$$

$$(2.19)$$

$$f_5(J_{\text{int}}, A, \delta, \phi) = R_{J_{\text{int}}-1}(J_{\text{int}}, A, \delta, \phi) - real(X_{J_{\text{int}}-1})$$

(2.20)

$$f_6(J_{\text{int}}, A, \delta, \phi) = I_{J_{\text{int}}-1}(J_{\text{int}}, A, \delta, \phi) - real(X_{J_{\text{int}}-1})$$

(2.21)

From above six non-linear equations, the three parameters are accurately estimated by Newton method and least squares. Using Newton method, the value of y in  $(k+1)^{\text{th}}$  iteration,  $y_{k+1}$ , is given by equation (2.22).

$$y_{k+1} = y_k - B_k \backslash F_k, \tag{2.22}$$

where "\" operator is the least squares operator,  $y_k$  is the vector containing the 3 estimated parameters in  $k^{\text{th}}$  iteration,  $F_k$  is the vector of  $f_1..f_6$  evaluated using estimated values in  $y_k$  and  $B_k$  is the Jacobean matrix evaluated using values in  $y_k$  as shown below.

$$B_{k} = \begin{bmatrix} \frac{\partial f_{1}}{\partial A} & \frac{\partial f_{1}}{\partial \delta} & \frac{\partial f_{1}}{\partial \phi} \\ \vdots & \vdots & \vdots \\ \vdots & & \\ \frac{\partial f_{6}}{\partial A} & \frac{\partial f_{6}}{\partial \delta} & \frac{\partial f_{6}}{\partial \phi} \end{bmatrix}_{y_{k}} \qquad F_{k} = \begin{bmatrix} f_{1} \\ \vdots \\ \vdots \\ f_{6} \end{bmatrix}_{y_{k}} \qquad y_{k} = \begin{bmatrix} A \\ \delta \\ \phi \end{bmatrix}_{k} \qquad (2.23)$$

It can be mentioned that this method always converges to a global minima as the initial points to start the iterations are very close to the actual values. Also, it can be

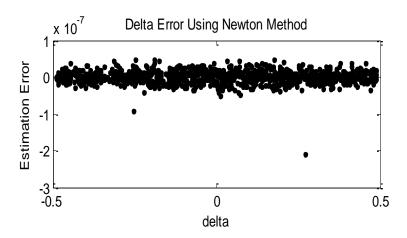

noticed that the number of operations in each iteration is no longer dependent on the length of the data record. Each iteration involves 6 equations and 3 unknowns, thus making the method more computationally efficient compared to other sine fitting methods [9-12] that use total data record for each iteration. Using rigorous simulation study, it is seen that a maximum of 5 iterations would always result in delivering precise values of the 3 parameters, thus, accurately estimating the fundamental. This accuracy in estimating the three parameters is limited by the noise power per bin (Fig. 2.7). The error in estimating the same 1000 values of  $\delta$ 's (as in Fig. 2.5) using this 2-step method is shown in Fig. 2.6. It can be seen that, the estimation error using the 2-step method is decreased by three orders (from  $10^{-4}$  to  $10^{-7}$ ) compared to that using equation (2.11). Also the error obtained using this method is only limited by the noise power per bin as shown in Fig. 2.7. A total of 50 randomly selected values of  $\delta$  for each value of SNR are considered and the error in estimating  $\delta$  is noted down. The data record length (M) for all runs is 4096. With constant data record length (M) and signal power, as the value of SNR increases, the noise power per bin decreases. It can be seen from Fig. 2.7 that, as the noise power per bin decreases (i.e., as SNR increases), the estimation error also decreases and more accurate values of  $\delta$  can be obtained. Hence, the proposed 2-step fundamental identification method accurately estimates the fundamental component and the accuracy is only limited by the noise power per bin. Let the final estimates of  $\delta$ , A and  $\phi$  be given as  $\hat{\delta}$ ,  $\hat{A}$  and  $\hat{\phi}$  respectively.

Figure 2.6: Error in estimating  $\delta$  versus actual value of  $\delta$  using 2-step method

Figure 2.7: Error in estimating  $\delta$  using 2-step method for different SNR values. With fixed signal power, as SNR increases, estimation error decreases

## **B)** Estimate the non-coherent fundamental

Using  $\hat{\delta}$ ,  $\hat{A}$  and  $\hat{\phi}$ , the non-coherent fundamental component in x[n] can be

estimated as  $x_nc[n]$  and is given as

$$x_n c[n] = A \cos\left(\frac{2\pi \left(J_{\text{int}} + \delta\right)}{M} n + \hat{\phi}\right)$$

(2.24)

## C) Construct a coherent fundamental

The fundamental component that is coherent (signal corresponding to  $J_{int}$  cycles) can be constructed using  $\hat{A}$  and  $\hat{\phi}$ , and is given as  $x_c[n]$  as shown in (2.25).

$$x_{c}[n] = A\cos\left(\frac{2\pi J_{\text{int}}}{M}n + \hat{\phi}\right)$$

(2.25)

## **D)** Fundamental Replacement

Using equations (2.24) and (2.25), the non-coherent fundamental can be removed from the output of ADC and replaced by a coherent fundamental. This replaced output is given as  $x_{new}[n]$  in equation (2.26).

$$x_{new}[n] = x[n] - x_n c[n] + x_c[n]$$

(2.26)

Since the non-coherent fundamental component in x[n] is replaced with a coherent fundamental in  $x_{new}[n]$ , taking FFT of  $x_{new}[n]$  gives accurate spectral results (SNR, SFDR, THD). Thus, the method can be used to perform full spectrum test without using windows and without large increase in area and test time (as shown in Simulation results).

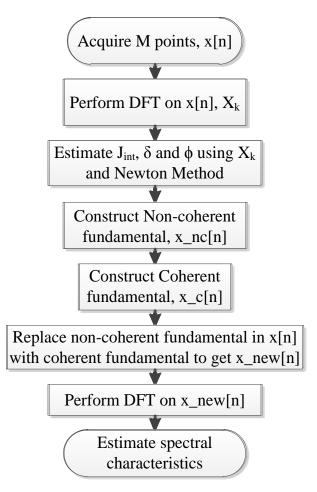

The flow chart in Fig. 2.8 summarizes the steps to be performed for spectral test using FIRE Method.

Figure 2.8: Flow Chart to perform spectral testing using proposed FIRE method

## IV. SIMULATION RESULS

In this section, simulation results to verify the functionality and robustness of the proposed FIRE method are presented. The computation time of the proposed method is also compared along with other methods used for non-coherent sampling. In Section IV and Section V, one data stream was used to estimate the spectral characteristics. The data record length was selected to accommodate the effect of noise.

#### A) Functionality

An 18-bit ADC was generated using MATLAB with an INL of 1.2 LSB. The true THD, SFDR and SNR values of the ADC are obtained by sending a pure sine wave that is coherently sampled. Later, a non-coherently sampled pure sine wave with same amplitude is sent to the same ADC and the proposed method is used to obtain spectral characteristics.

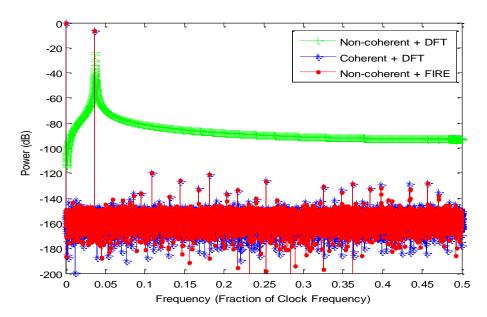

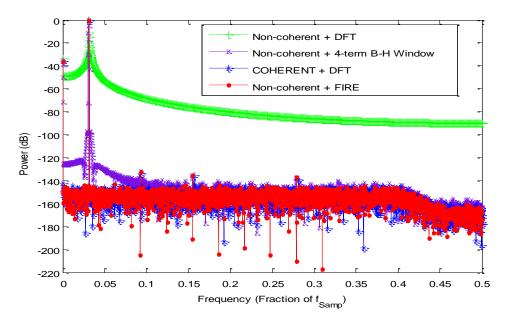

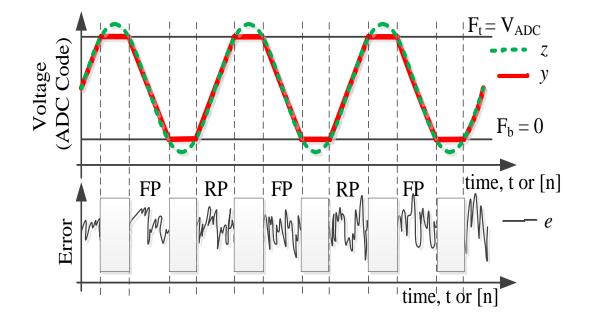

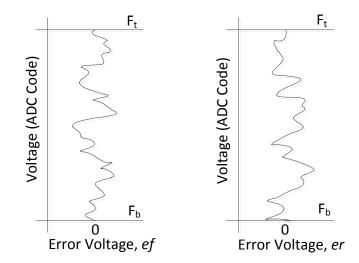

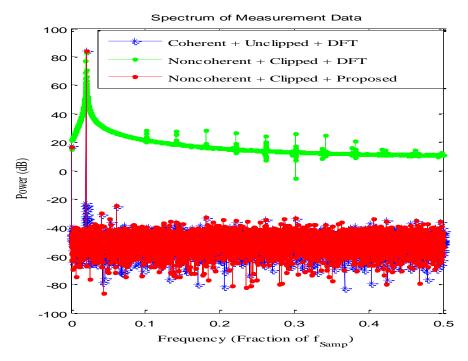

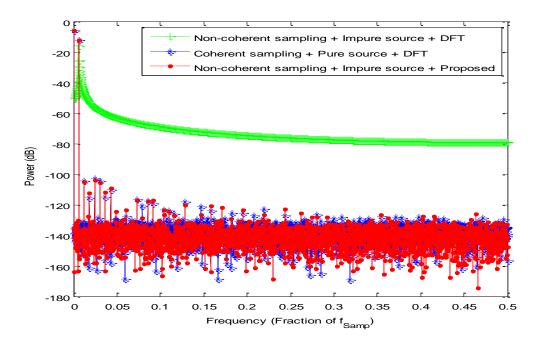

Fig. 2.9 shows three spectrums of the same ADC obtained using the following cases. The Blue spectrum is obtained when the ADC is coherently sampled with M = 16384 and J = 593.00. The spectrum is clean without any leakage. The other two spectrums are obtained using non-coherently sampled data with J = 593.1237. The Green spectrum is obtained when DFT is directly performed on the non-coherently sampled data. As expected, there is severe leakage in the spectrum due to non-coherently sampled data, the leakage is completely eliminated as shown in the Red spectrum. It can also be seen that the red spectrum exactly matches with the Blue spectrum. Table 2.1 lists the spectral results estimated using the proposed method on non-coherently sampled data and the coherently sampled method. It can be seen that the results obtained from non-coherently sampled data using FIRE method are very close to those obtained using coherent sampling method. This shows that the proposed method accurately estimates the spectral characteristics even when an input signal is not coherently sampled.

Figure 2.9: Plot showing the spectrum of an ADC for three cases. Blue spectrum is obtained using Coherent sampling ( $J_{int} = 593$ ), Red spectrum is obtained using the proposed FIRE method on non-coherently sampled data (J = 593.1237) and Green spectrum is obtained after performing DFT on the same non-coherently sampled data.

| Method                | THD<br>(dB) | SFDR<br>(dB) | SNR<br>(dB) |

|-----------------------|-------------|--------------|-------------|

| <b>Coherent + DFT</b> |             |              |             |

| (Ideal)               | -110        | 113.7        | 108.5       |

| Non-coherent +        |             |              |             |

| FIRE                  | -109.7      | 113.6        | 108.6       |

TABLE 2.1: Spectral Results of 18-bit ADC corresponding to Fig. 2.9

## **B)** Robustness

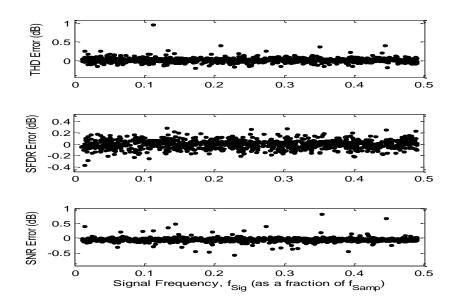

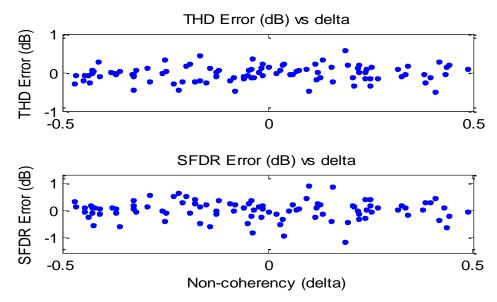

The robustness of the method with signal frequency and non-coherency is also presented. An 18-bit ADC with INL of 2.4 LSB was simulated. 1000 values of  $\delta$  and  $J_{int}$ corresponding to input signal are randomly generated. The values of  $\delta$  and  $J_{int}$  range from -0.5 to 0.5 (the whole range of  $\delta$ ) and from 0 to M/2 (whole Nyquist range)

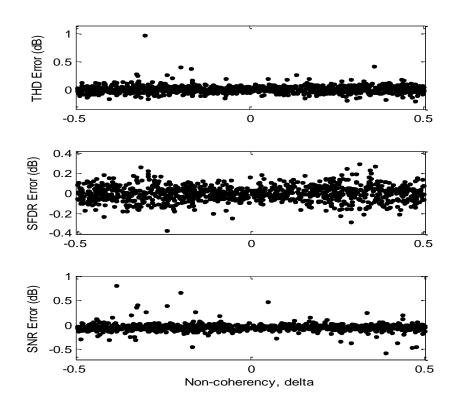

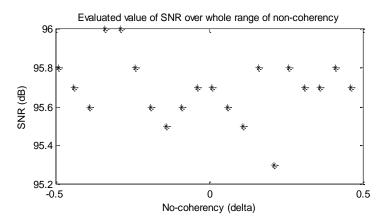

respectively. The THD, SFDR and SNR of the ADC obtained by coherent sampling are -104.2dB, 107.5dB and 108dB respectively. The errors obtained in estimating the THD, SFDR and SNR values of the ADC with respect to signal frequency (given as a fraction of sampling frequency) are shown in Fig. 2.10. It can be seen that the values are very accurately estimated and the method is robust for input signal frequency in the whole Nyquist range. Fig. 2.11 shows the errors in THD, SFDR and SNR with respect to noncoherency,  $\delta$ . The errors are attributed due to several factors such as noise, the accuracy with which the parameters are estimated and also the change in spectral parameters due to slight change in frequency (as changing  $\delta$  changes the input frequency). It can also be seen that the method is robust over the whole range of  $\delta$ , from -0.5 to 0.5. Hence, the method is robust for input signal frequencies in the whole Nyquist range and for any non-coherency.

Figure 2.10: Error in estimating THD, SFDR and SNR over the whole range of input signal frequency (From DC to Nyquist range)

Figure 2.11: Error in estimating THD, SFDR and SNR over the whole range of noncoherency in the fundamental,  $\delta$  (From -0.5 to 0.5)

## **C)** Computation Time

The calculation time complexity of the proposed method is of the order of M\*log<sub>2</sub>M, since, performing FFT is the only major time consuming block. The time taken by the proposed FIRE method is compared with different windows, the best data record length method [23] and a Four parameter sine fitting method [8] in Table 2.2 (using MATLAB on a 64-bit, Intel Core i5 CPU with 4GB memory). It can be seen that of all the methods listed, the proposed method provides accurate test results with least computation time. The method in [23] consumes more time as the best data record length

is not necessarily a power of 2. This results in larger computation time for the FFT algorithm in [23]. It can also be seen from the table that only one window can accurately test an 18-bit ADC while the other three windows cannot be used to test. This shows the dependency of results on the type of window used. As a result, prior knowledge about the resolution of ADC is required to perform spectral test using windows. The computation time using a Four-parameter sine-wave fitting method using time domain data and nonlinear least squares method is shown. Though the method provides accurate estimates of fundamental, it can be seen that using all time-domain data consumes large computation time. As a result, the proposed FIRE method can be readily used to test any resolution ADC to obtain fast and accurate spectral results.

| - 1.1200/                    |          |                               |  |  |  |

|------------------------------|----------|-------------------------------|--|--|--|

| Method                       | Time     | Functionality                 |  |  |  |

| Proposed Method              | 1.7 ms   | Accurate                      |  |  |  |

| Best Data Record Method [23] | 27.8 ms  | Accurate                      |  |  |  |

| Window 2 in [29]             | 2.9 ms   | Accurate                      |  |  |  |

| Blackman Harris (4-term)     | 0.7 ms   | Inaccurate                    |  |  |  |

| Hanning                      | 0.5 ms   | Inaccurate                    |  |  |  |

| Hamming                      | 0.9 ms   | Inaccurate                    |  |  |  |

| * Four Parameter Sine Fit    | >25.2 ms | Occasional<br>Inaccurate SFDR |  |  |  |

| (Nonlinear Least Squares)    |          |                               |  |  |  |

TABLE 2.2: Comparison of Calculation Time (J=519.379, M = 8192, 18-bit ADC, INL = 1.4LSB)

\*: Time taken to only estimate the fundamental accurately. Later, 3-parameter fit is required to estimate each harmonic using the total 8192 points which results in more computation time (Clause 8.8.1.3 of [8]).

#### V. MEASUREMENT RESULTS

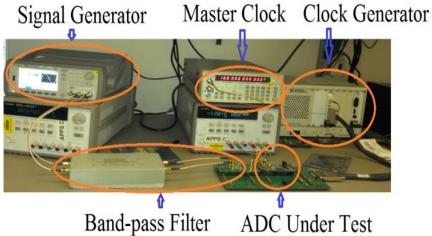

In this section, measurement data is used to validate the effectiveness of the proposed FIRE method. Two commercially available ADCs are tested for spectral characteristics with non-coherent sampling using the FIRE method. The first ADC is ADS1282 which is a very high resolution delta-sigma ADC with an SNR of 120dB. This ADC is used to verify the functionality of FIRE method for very high resolution ADCs. The second ADC is ADS8318 which is a 16-bit, 500 kSPS Successive Approximation Register (SAR) ADC. This ADC is used to verify the robustness of proposed FIRE method with respect to whole range of non-coherency,  $\delta$ , using measurement data.

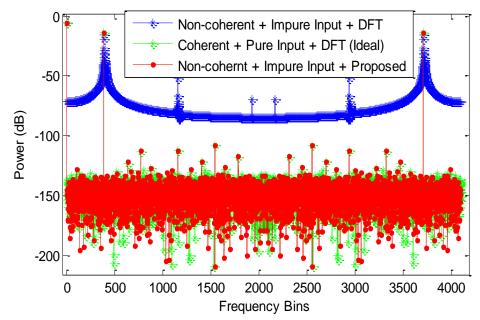

## A) ADS1282 Test (Functionality)

Fig.2.12 shows the test setup used to test ADS1282. DAC1282 is used to provide the pure input signal to test ADC. Both the DAC and ADC are controlled by the same master clock. The ADC sampling clock frequency is 1 kHz and the input signal frequency for coherent sampling is 31.25 Hz. A total of 4096 points were sampled (*M*). The value of *J* obtained is 128 for coherent sampling. With this setup, a clean spectrum is obtained and is given by the blue plot in Fig. 2.13. Later, the same ADC is noncoherently sampled with signal frequency given by 30.952 Hz, which results in *J* equal to 126.781. This corresponds to non-coherent sampling with  $\delta$ =-0.219. The spectrum of the output of ADC when FFT is applied on this data is given by the green plot in Fig. 2.13. As expected there is severe spectral leakage. However, using the proposed FIRE method on this non-coherently sampled data resulted in a clean and accurate spectrum as shown by the Red plot in Fig. 2.13. It can be seen that the Red spectrum (FIRE) matches

with the Blue spectrum (Coherent) and provides accurate spectral results for a very high resolution ADC. To show the effect of windows on spectral testing, the spectrum obtained when a 4-term Blackman Harris window is used on the same non-coherently sampled data is shown by the purple plot in Fig. 2.13. Blackman Harris window is used here as it is one of the most widely used windows for testing. Table 2.3 compares the values of THD, SFDR and SNR of the ADC using the FIRE method and windows method with the values obtained using Coherent sampling method. It can be seen that the FIRE method accurately estimates the parameters. From the purple plot in Fig. 2.13 and from Table 2.3, it can be said that 4-term Blackman Harris window cannot be used for testing this high resolution ADC. Hence, as mentioned earlier, the choice of window used is dependent on the resolution of ADC.

Figure 2.12: Test setup for ADS1282 ( $f_{Samp} = 1 \text{ kHz}$ , M = 4096,  $J_{coherent} = 128$ ,  $J_{noncoherent} = 126.781$ )

| TABLE 2.3: SPECTRAL CHARACTERISTICS OF ADS1282 MEASURED USING COHERENT |

|------------------------------------------------------------------------|

| AND NON-COHERENT SAMPLING (IN dB)                                      |

| METHOD                           | THD    | SFDR  | SNR   |

|----------------------------------|--------|-------|-------|

| Coherent                         | -130.9 | 133.4 | 120.3 |

| Non-coherent + FIRE              | -129.6 | 132.3 | 120.1 |

| Non-coherent + 4-term B-H Window | -126.5 | 130.8 | 90.5  |

Figure 2.13: Plot showing Spectrum of ADS1282 for 4 different cases. The Blue spectrum is obtained with coherent sampling (J = 128). The Red spectrum is obtained when FIRE method is used on non-coherently sampled data (J = 126.781). The Green spectrum is obtained when DFT is performed on non-coherently sampled data. The purple spectrum is obtained when a 4-term Blackman-Harris (B-H) window is used on the non-coherently sampled data.

#### **B)** ADS8318 Test (Functionality and Robustness)

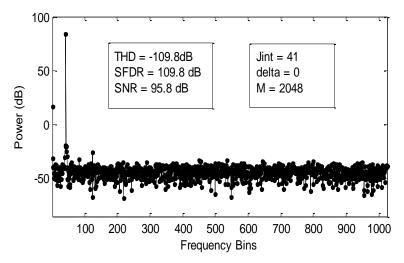

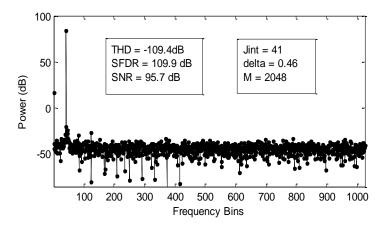

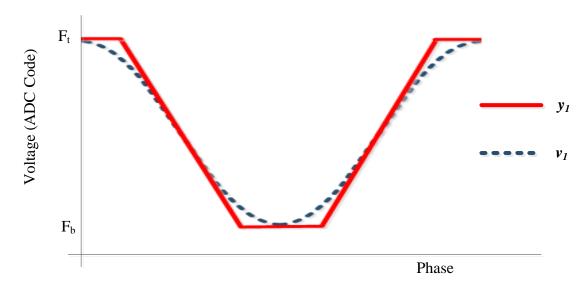

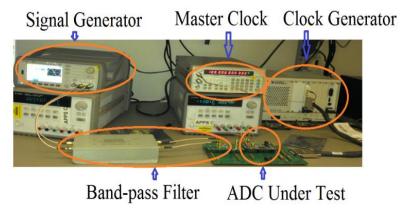

The second ADC that is tested is ADS8318. The test setup is as shown in Fig. 2.14. A signal generator is followed by two band pass filters with center frequency at 10 kHz. The output of the filter is fed to the input of ADC. The ADC is clocked at 500 kSPS and a total of 2048 samples were collected. The input signal frequency to achieve coherent sampling is given by 10.009765625 kHz which gives a value of *J* equal to 41. Fig. 2.15 shows the values of THD, SFDR and SNR along with the spectrum of ADS8318 with coherent sampling. For a value of  $\delta = 0.46$ , Fig. 2.16 shows the spectrum of the same ADC using FIRE method. It can again be seen that there is no leakage in the

44

spectrum in spite of non-coherent sampling and the spectral parameters are very accurately estimated.

Figure 2.14: Test Setup for ADS8318

Figure 2.15: Spectrum of ADS8318 using Coherent Sampling

Figure 2.16: Spectrum of ADS8318 using Non-coherent sampling and Proposed FIRE method

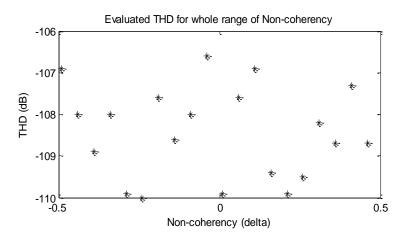

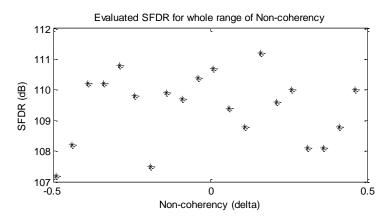

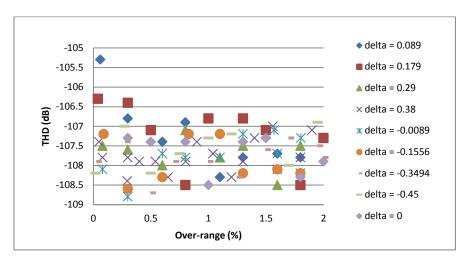

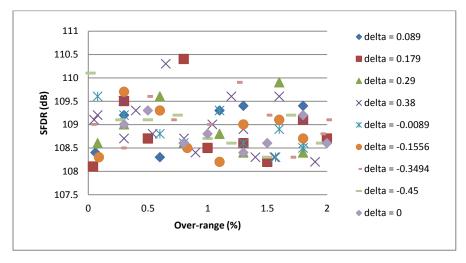

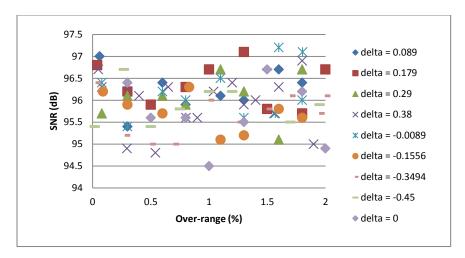

Later, to test for robustness of the FIRE method for any value of non-coherency ( $\delta$ ) using measurement data, the frequency of input signal is changed from 9.887 kHz to 10.132 kHz so that the value of *J* varies from 40.5 to 41.5. This covers the whole range of  $\delta$  from -0.5 to 0.5. The values of THD, SFDR and SNR are evaluated for each case and plotted in Fig. 2.17, Fig. 2.18 and Fig. 2.19 respectively. The variation of THD, SFDR and SNR for different values of  $\delta$  is expected as only 2048 points are sampled to test a 16 bit ADC. It can be seen that the values of THD, SFDR and SNR and SNR are very accurately estimated using the proposed FIRE method for any value of non-coherency,  $\delta$ .

Hence, the functionality and robustness of the proposed FIRE method with noncoherent sampling is successfully validated using measurement data from two high resolution ADCs.

Figure 2.17: Measured THD values over whole range of  $\delta$  for ADS8318

Figure 2.18: Measured SFDR values over whole range of  $\delta$  for ADS8318

Figure 2.19: Measured SNR values over whole range of  $\delta$  for ADS8318

#### VI. CONCLUSION

A new Fundamental Identification and Replacement (FIRE) test method was proposed that completely eliminates the requirement of coherent sampling for full spectrum test. A two-step method using DFT and Newton method was described to accurately identify the non-coherent fundamental. It was shown that the accuracy with which the fundamental was identified is only limited by the noise power per bin  $(P_{noise}/M)$ . As a result, the method can be readily used to test any ADC output without prior knowledge about the resolution of ADC, unlike windowing method. Simulation results were presented to show the functionality and robustness of the proposed FIRE method with respect to any non-coherency ( $\delta$ ) and to any input signal frequency in the whole Nyquist range. The time complexity of the method is of the order of M\*log<sub>2</sub>(M). Thus, all the issues related to previous state of-the art techniques such as, large computation time, large area, lack of robustness of the method over the whole Nyquist range, dependency of the results on the window chosen and inability to perform full spectrum test, have been addressed in the proposed FIRE method. Furthermore, measurement results using two commercially available high resolution ADCs were presented that validated the accurate functionality and robustness of the FIRE method. Finally, it can be said that the FIRE method can be used in all forms of test such as Bench characterization, Final test and BIST, to save the cost and effort associated with achieving coherent sampling.

#### VII. ACKNOWLEDGMENTS

I would like to thank Ken Butler, Mojtaba Nowrozi, Rafael Ordonez and Mark Berarducci from Texas Instruments for providing help in obtaining the measurement data to verify the proposed method.

Materials presented in this chapter are based upon the work supported in part by the National Science Foundation, the Semiconductor Research Corporation and Texas Instruments Inc. Any opinions, findings and conclusions or recommendations expressed in this chapter are those of the authors and do not necessarily reflect the views of the sponsors.

## References

- [1] F.J. Harris, "On the use of Windows for Harmonic Analysis with the Discrete Fourier Transform", *Proceedings of the IEEE*, Vol. 66, No. 1, 1978.

- [2] P. Carbone, E. Nunzi, D. Petri, "Windows for ADC Dynamic Testing via Frequency-Domain Analysis," *IEEE Trans. Instr. & Meas.*, 50(6), pp 1571-1576, 2001

- [3] S. Raze, D. Dallet, P. Marchegay, "Non coherent spectral analysis of ADC using FFT windows: an Alternative Method", *IEEE Workshop on Intelligent Data Acquisition and Advanced Computing systems*, Sept., 2005

- [4] D. Belega, M. Ciugudean, D. Stoiciu, "Choice of the cosine-class windows for ADC dynamic testing by spectral analysis", *Measurement* Vol. 40, no. 4, pp. 361-371, 2007.

- [5] *Maxim Integrated Application Note 1040*, "Coherent Sampling vs. Window Sampling".

- [6] O.M. Solomon Jr., "The Use of DFT Windows in Signal-to-Noise Ratio and harmonic Distortion Computations", *IEEE Trans. Instr. & Meas.*, 43(2), pp 194-199, 1994

- [7] S. Sudani, M. Wu, D. Chen, "A Novel Robust and Accurate Spectral Testing Method for Non-coherent Sampling", in *Proc. ITC 2011*, pp 1-10.

- [8] IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters, IEEE Std. 1241-2010

- [9] T.Z. Bilau, T. Megyeri, A. Sarhegyi, J. Markus, I. Kollar, "Four Parameter Fitting of Sine Wave Testing Result: Iteration and Convergence", *Computer Standards and Interfaces*, Vol. 26, pp. 51-56, 2004.

- [10] R. Pintelon, J. Schoukens, "An Improved Sine-Wave Fitting Procedure for Characterizing Data Acquisition Channels", *IEEE Trans. Instr. & Meas.*, Vol. 45, No. 2, pp 588-593, 1996

- [11] K.F. Chen, "Estimating Parameters of a Sine Wave by Separable Nonlinear Least Squares Fitting", *IEEE Trans. Instr. & Meas.*, Vol. 59, No. 12, pp 3214-3217, 2010

- [12] G. Simon, R. Pintelon, L. Sujbert, J. Schoukens, "An Efficient Nonlinear Least Square Multisine Fitting Algorithm", *IEEE Trans. Instr. & Meas.*, Vol. 51, No. 4, pp 750-755, 2002

- [13] G. D'Antona, A. Ferrero, "Digital Signal Processing for Measurement Systems Theory and Applications", 2006 Springer Science + Business Media, Inc.

- [14] X.M. Gao, et al, "Analysis of second-order harmonic distortion of ADC using bispectrum", *IEEE Trans. Instr. & Meas.*, 45(1), pp. 50-55, 1996.

- [15] J.Q. Zhang and S.J. Oyaska, "ADC Characterization based on singular value decomposition", *IEEE Trans. Instr. & Meas.*, 51(1), 2002

- [16] C. Rebai, D. Dallet, P. Marchegay, "Noncoherent Spectral Analysis of ADC Using Filter Bank", *IEEE Trans. Instr. & Meas.*, Vol. 53, No. 3, pp 652-660, 2004

- [17] Y. Liu, L. Zhu, B. Zhan, "Noncoherent Spectral Analysis of ADC Using Resampling Method", *IEEE International Conference on Testing and Diagnosis*, ICTD 2009.

- [18] D.K. Mishra, "ADC testing using interpolated fast fourier transform (IFFT) technique", *International Journal of Electronics*, 90:7, 459-469.

- [19] J. Schoukens, R. Pintelon, H. Van hamme, "The Interpolated Fast Fourier Transform: A Comparative Study", ", *IEEE Trans. Instr. & Meas.*, Vol. 41, No. 2, pp 226-232, 1992

- [20] D. Belega, D. Dallet, "Multipoint Interpolated DFT Method for Frequency Estimation", *International Multi-Conference on Systems, Signals and Devices, 2009.*

- [21] D. Belega, D. Dallet, D. Petri, "Estimation of the Effective Number of Bits of ADCs Using the Interpolated DFT Method", *IEEE Instrumentation and Measurement Technology Conference*, 2010.

- [22] D. Belega, D. Dallet, D. Stoiciu, "Choice of the Window Used in the Interpolated Discrete Fourier Transform Method", *Revue Roumaine des Sciences Techniques Serie Electrotechnique et Energetique*, Vol. 54, No. 4, 2009, 365–374.

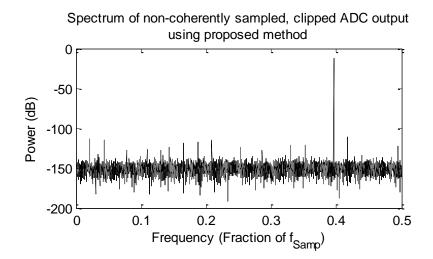

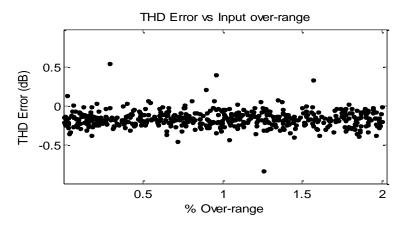

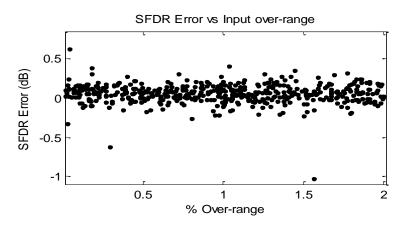

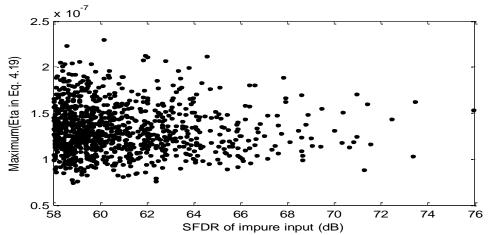

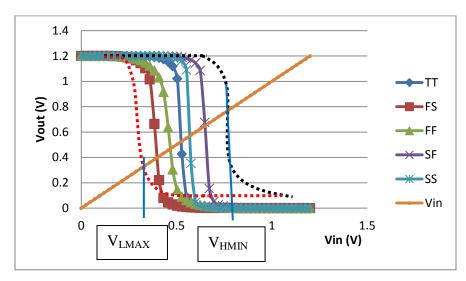

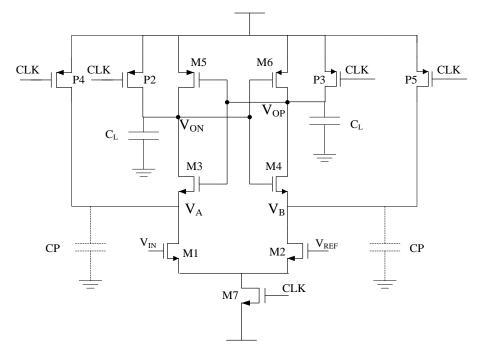

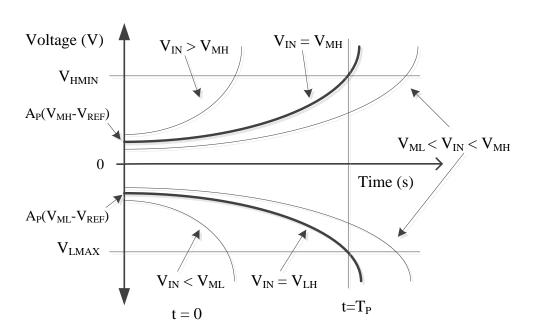

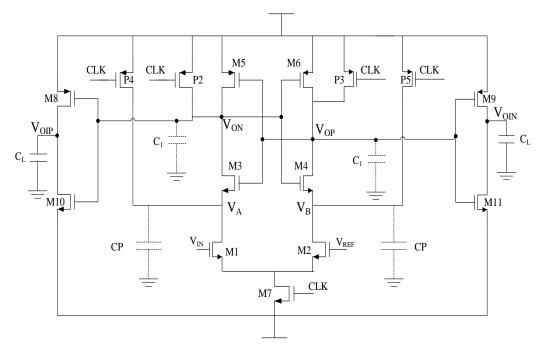

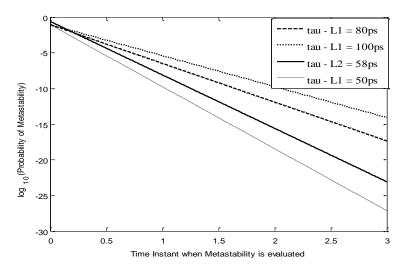

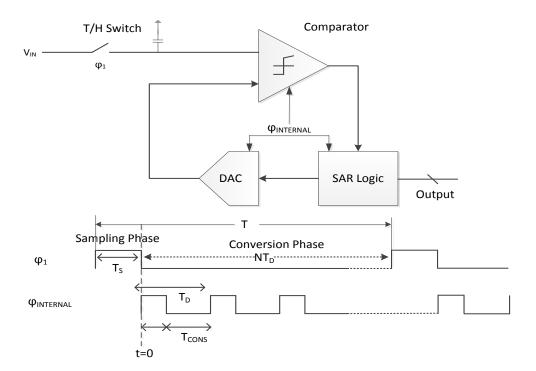

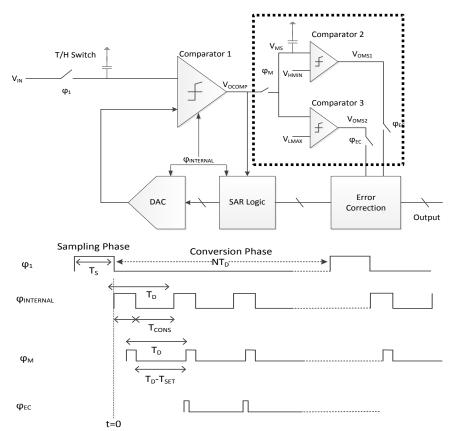

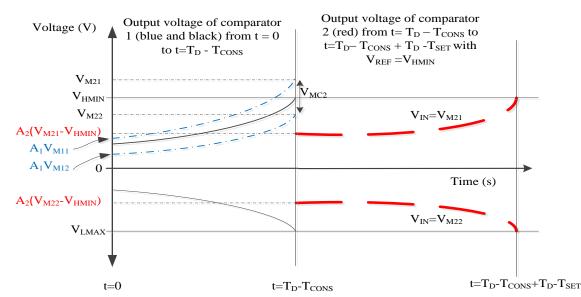

- [23] Z. Yu, D. Chen, and R. Geiger, "A computationally efficient method for accurate spectral testing without requiring coherent sampling," in *Proc ITC*, 2004, pp. 1398– 140.